# **Department Of electrical and computer Engineering**

# ADVANCED DIGITAL SYSTEMS DESIGN

# ENCS3310

**Project report**

Instructor: Dr. Abdallatif Abulssa

Made By: Islam Jihad

ID: 1191375

Section 2

Date: 25/Nov/2021

# Table of Contents

| Table of figures   3                     |

|------------------------------------------|

| Brief Introduction and Background4       |

| Design philosophy                        |

| Basic Gates                              |

| 1-bit Full Adder:                        |

| 8-bit Full-Adder:9                       |

| Magnitude Comparator in digital logic:10 |

| 1-Bit Magnitude Comparator10             |

| 2-Bit Magnitude Comparator11             |

| Stage 1                                  |

| Stage 2                                  |

| D-Flip Flop18                            |

| Test Generator19                         |

| Result Analyzer                          |

| Built in Self-Test                       |

| Results                                  |

| <ul> <li>Stage 1</li></ul>               |

| <ul> <li>Stage 2</li></ul>               |

| Conclusion and Future works24            |

| References                               |

| Appendix                                 |

# Table of figures

| Figure 1:used gates with delay                                      | 7  |

|---------------------------------------------------------------------|----|

| Figure 2: 1bit Full Adder is implemented using AND,OR and XOR gates | 7  |

| Figure 3: full adder code                                           | 8  |

| Figure 4:Complete 8-bit Adder                                       |    |

| Figure 5: 8-bit full adder code                                     | 9  |

| Figure 6:1 bit magnitude comparator                                 | 10 |

| Figure 7:1-bit magnitude comparator code                            |    |

| Figure 8:: 2 bit magnitude comparator                               | 11 |

| Figure 9:2bit magnitude comparator code                             | 12 |

| Figure 10:comparator truth table                                    | 13 |

| Figure 11:comparator stage 1 code                                   | 14 |

| Figure 12: stage1 output                                            | 15 |

| Figure 13:Comparatore stage2 code                                   | 16 |

| Figure 14:stage2 output                                             | 17 |

| Figure 15:d-flip flop truth table                                   | 18 |

| Figure 16: d flip-flop code                                         | 18 |

| Figure 17:test code                                                 | 19 |

| Figure 18:result analyzer code                                      | 20 |

| Figure 19:Built In Self Test code for adder comparator              | 21 |

| Figure 20:Built In Self-Test code for magnitude comparator          | 21 |

| Figure 21:simulation outcomes                                       | 22 |

| Figure 22:outcome of the simulation                                 | 23 |

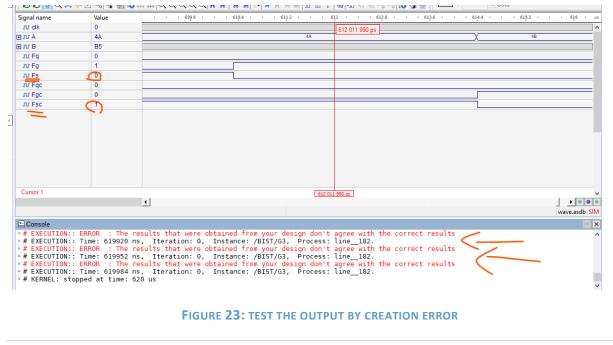

| Figure 23: test the output by creation error                        | 23 |

|                                                                     |    |

# Brief Introduction and Background

We'll build a signed 8-bit comparator in two parts in this project. This system will be made up of little entities that will also be made up of a small number of entities. Table 1 shows how we'll employ the fundamental gates with various delays. Regardless of the number of inputs, the fundamental gates have the same delay.

| Gate     | Delay |

|----------|-------|

| Inverter | 2 ns  |

| NAND     | 5 ns  |

| NOR      | 5 ns  |

| AND      | 7 ns  |

| OR       | 7 ns  |

| XNOR     | 9 ns  |

| XOR      | 12 ns |

We will create a 1-bit full adder using the basic gates listed above, and then an 8-bit full adder/subtractor, which may be used to implement the adder comparator approach.

And we will create a 1-bit magnitude comparator and 2- bit too, it will be used in the second stage.

The two stages that we will build the system: first, the full adder subtraction as a comparator, is using an adder with (ripple and/or look ahead) full adder 8 times. And the second stage is the magnitude comparator, we had learned them in Digital course.

We will calculate the duration of delay for each stage to use in testing the outputs.

For each step, there will be a Built-In Self-Test (BIST) with two registers: The first register is the test generator, which sends the inputs to our system and sends the outputs to the second register, which has a clock input. The second register is the Result analyzer, which receives the behavioral output from the test generator and the system's output, and ensures that the two outputs are correct.

We will simulate our system, test it, and ensure that the outputs are valid using Aldec Active-HDL Student Edition.

# Design philosophy Basic Gates

First, we created the basic gates as shown in Figure 1. There was an idea to create a single entity for each basic gate and make it generic with a N variable that determines the number of inputs, but it is difficult to construct and call the gate entity in other entities. On the other hand, we made the needed gates that need more than 2 inputs with the same delay to reduce delay.

48

49

50

55

61

62

63 64

65 66

67 68

69

77 78

79

80

81 82

83

84

85 86

87

88

89

90

91

92

93

```

library ieee;

USE ieee.std_logic_1164.ALL;

3

4

entity Inverter is

port(a: in std_logic;

b: out std_logic);

5

6

7

8

9

end entity Inverter;

architecture strct of Inverter is

begin

11

b<= not a after 2 ns;</pre>

12

13

end architecture strct;

14

15

16

17

18

library ieee;

USE ieee.std_logic_1164.ALL;

19

20

entity NANDG is

21

22

port(a,b: in std_logic;

c: out std_logic);

23

24

25

26

27

28

29

end entity NANDG;

architecture strct of NANDG is

begin

c<= a nand b after 5 ns;</pre>

end architecture strct;

30

31

32

33

library ieee;

34

USE ieee.std_logic_1164.ALL;

35

36

entity NORG is

port(a,b: in std_logic;

c: out std_logic);

37

39

end entity NORG;

40

41

architecture strct of NORG is

42

begin

43

c<= a nor b after 5 ns;</pre>

44

45

end architecture strct;

```

46

```

library ieee;

USE ieee.std_logic_1164.ALL;

entity ANDG is

port(a,b: in std_logic;

c: out std_logic);

end entity ANDG;

architecture strct of ANDG is

begin

c<= a and b after 7 ns;</pre>

end architecture strct;

library ieee;

USE ieee.std_logic_1164.ALL;

entity ORG is

port(a,b: in std_logic;

c: out std_logic);

end entity ORG;

architecture strct of ORG is

begin

c<= a or b after 7 ns;</pre>

end architecture strct;

library ieee;

USE ieee.std_logic_1164.ALL;

entity XNORG is

port(a,b: in std_logic;

c: out std_logic);

end entity XNORG;

architecture strct of XNORG is

begin

c<= a xnor b after 9 ns;</pre>

end architecture strct;

```

```

128

129

130

131

library ieee;

USE ieee.std_logic_1164.ALL;

entity OR3G is

port(a,b,d: in std_logic;

c: out std_logic);

end entity OR3G;

96

97

library ieee;

\begin{array}{c} 1323\\ 1334\\ 1355\\ 136\\ 137\\ 138\\ 139\\ 140\\ 141\\ 142\\ 143\\ 144\\ 145\\ 144\\ 145\\ 151\\ 152\\ 153\\ 156\\ 157\\ 158\\ 159\\ 160\\ 161\\ 162\\ 163\\ 166\\ 167\\ 168\\ \end{array}

98

USE ieee.std_logic_1164.ALL;

99

entity XORG is

port(a,b: in std_logic;

c: out std_logic);

100

architecture strct of OR3G is

begin

c<= a or b or d after 7 ns;

101

102

end entity XORG;

end architecture strct;

104

105

architecture strct of XORG is

library ieee;

USE ieee.std_logic_1164.ALL;

106

begin

107

c<= a xor b after 12 ns;</pre>

entity XOR_subG is

port(a: in std_logic_vector(7 downto 0);

c: out std_logic_vector(7 downto 0));

end entity XOR_subG;

108

109

end architecture strct;

110

111

architecture strct of XOR_subG is

112

113

begin

c<= a xor "llllllll" after 12 ns;</pre>

library ieee;

114

115

116

USE ieee.std_logic_1164.ALL;

end architecture strct;

entity AND3G is

port(a,b,d: in std_logic;

c: out std_logic);

library ieee;

USE ieee.std_logic_1164.ALL;

117

118

entity NOR8G is

119

120

end entity AND3G;

port(a: in std_logic_vector(7 downto 0);

c: out std_logic);

end entity NOR8G;

121

122

architecture strct of AND3G is

begin

architecture strct of NOR8G is

c<= a and b and d after 7 ns;</pre>

123

signal s: std_logic;

124

169

170

171

begin

125

end architecture strct;

s<= a(0) or a(1) or a(2) or a(3) or a(4) or a(5) or a(6) or a(7);

c<= not s after 5 ns;

end architecture strct;

126

127

******************************

```

FIGURE 1:USED GATES WITH DELAY

## 1-bit Full Adder:

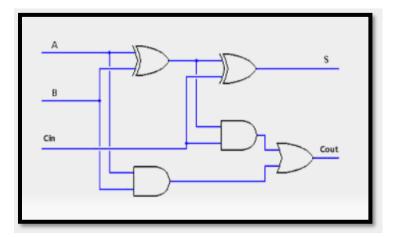

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It has two inputs: X and Y, that represent the two significant bits to be added, and a Z input that is a carry-in from the previous significant position. It has two outputs: S which is the sum of the two input bits which can be 0-3 and Z to carry the value in case the output from S is 2 or 3 because the binary forms of these require two digits for their representation.[2]

FIGURE 2: 1BIT FULL ADDER IS IMPLEMENTED USING AND, OR AND XOR GATES

```

-- one bit full adder circuit

2

library ieee;

3

USE ieee.std_logic_1164.ALL;

4

5

6

entity FA is

7

port(A,B,Cin:in std_logic;

8

s,Cout:out std logic);

9

10

end entity FA;

11

12

13

architecture one bit adder of FA is

14

signal s1,s2,s3,s4,s5: std_logic;

15

begin

16

gl: entity work.XORG(strct) port map(A,B,sl);

17

g2: entity work.ANDG(strct) port map(A,B,s2);

g3: entity work.ANDG(strct) port map(Cin,s1,s3);

18

19

g4: entity work.XORG(strct) port map(s1,Cin,s4);

20

g5: entity work.ORG(strct) port map(s2,s3,s5);

21

22

s<=s4;

23

Cout<=s5;

24

--24 ns needed to give correct answer

25

26 end architecture one_bit_adder;

```

FIGURE 3: FULL ADDER CODE

This full adder is constructed as shown in Figure 3 to be utilized later in the construction of a 8bit full adder. The maximum delay time was 24 ns.

### 8-bit Full-Adder:

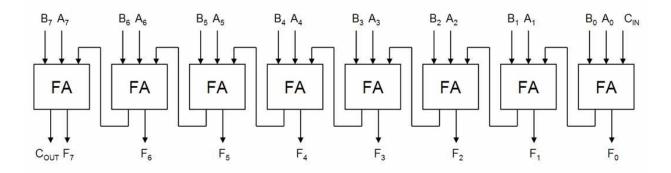

I take 8 of these full adders(1-bit full adder), and combine them to create an 8-bit Adder. In an 8 bit adder the full adders are connected in a cascade with a 1 carry cascading from a least significant bit to the most significant bit.[2]

FIGURE 4:COMPLETE 8-BIT ADDER

And the carry out of the last bit and the one before to get the overflow from them later, the delay that needed in this circuit was 24 ns only! It looks like it worked as a lookahead.

The code of the circuit is shown below.

```

42

--8 bits full adder

43

44

library ieee;

45

USE ieee.std_logic_1164.ALL;

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

entity bit8_adder is

port(A,B:in std_logic_vector(7 downto 0);

Cin:in std_logic;

sum:out std_logic_vector(7 downto 0);

Cout6, Cout:out std_logic);

end entity bit8 adder;

architecture strct of bit8_adder is

signal s,c:std_logic_vector(7 downto 0);

begin

62

gl: entity work.FA(one_bit_adder) port map(A(0),B(0),Cin,s(0),c(0))

g2: entity work.FA(one_bit_adder) port map(A(1),B(1),c(0),s(1),c(1));

g3: entity work.FA(one_bit_adder) port map(A(2),B(2),c(1),s(2),c(2));

63

64

g4: entity work.FA(one_bit_adder) port map(A(3),B(3),c(2),s(3),c(3));

g5: entity work.FA(one_bit_adder) port map(A(4),B(4),c(3),s(4),c(4));

65

66

g6: entity work.FA(one_bit_adder) port map(A(5),B(5),c(4),s(5),c(5));

g7: entity work.FA(one_bit_adder) port map(A(6),B(6),c(5),s(6),c(5));

g8: entity work.FA(one_bit_adder) port map(A(7),B(7),c(6),s(7),c(7));

67

68

69

70

71

72

Cout6<=c(6);

Cout<=c(7);

sum<=s;

-- 24 ns needed for delay correction

75

end architecture strct:

```

FIGURE 5: 8-BIT FULL ADDER CODE

### Magnitude Comparator in digital logic:

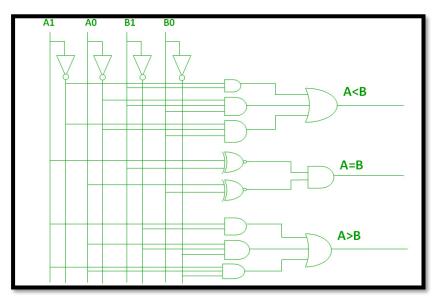

It's a combinational circuit that compares two digital or binary numbers in order to find out whether one binary number is **equal**, **less than** or **greater than** the other binary number. I logically design a circuit for which we will have two inputs one for A and other for B and have three output terminals, one for A > B condition, one for A = B condition and one for A < B condition. [1]

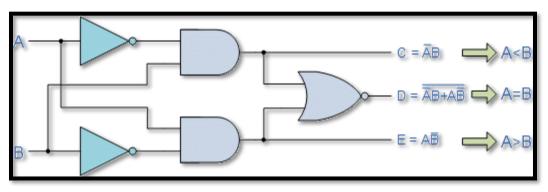

### 1-Bit Magnitude Comparator

A single bit comparator used to compare two bits. It consists of two inputs each for two single bit numbers and three outputs to generate less than, equal to and greater than between two binary numbers. [1]

FIGURE 6:1 BIT MAGNITUDE COMPARATOR

The following figure show the code. The delay was 14 ns which is good.

```

6

library ieee;

USE ieee.std_logic_1164.ALL;

7

8

9

entity one_bit is

port(a,b: in std_logic;

F:out std_logic_vector(2 downto 0));

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

end entity one_bit;

architecture strct of one_bit is

signal s1,s2,s3,s4,s5:std_logic;

begin

gl: entity work.Inverter(strct) port map(A,sl);

g2: entity work.Inverter(strct) port map(B,s2);

g3: entity work.ANDG(strct) port map(B,s1,s3);

g4: entity work.ANDG(strct) port map(A,s2,s4);

--A<B

--A>B

g5: entity work.NORG(strct) port map(s3,s4,s5); --A=B

28

F<=(s5 & s3 & s4);

29

-- 14 ns delay

30

31

end architecture strct;

```

### 2-Bit Magnitude Comparator

This comparator used to compare two binary numbers each of two bits. It consists of four inputs and three outputs to generate less than, equal to and greater than between two binary numbers. [1]

I used the gates that we made with their delay to compare it with physical and real life.

FIGURE 8:: 2 BIT MAGNITUDE COMPARATOR

Here is the code picture, the delay was 16 ns which is good

```

41

library ieee;

42

43

USE ieee.std_logic_1164.ALL;

44

45

entity two bit is

port(Fin: in std_logic_vector(2 downto 0);

al,a0,bl,b0: in std_logic;

Fout:out std_logic_vector(2 downto 0));

46

47

48

49

end entity two_bit;

50

51

52

53

architecture strct of two bit is

54

55

signal na1,na0,nb1,nb0:std logic;

signal a:std_logic_vector(5 downto 0);

signal n:std_logic_vector(1 downto 0);

56

57

signal smaller, equall, greater: std_logic;

signal f: std_logic_vector(2 downto 0);

58

59

60

61

begin

62

63

-- compare if the previous bits are greater to pass the answer or not to start calculating

Fout<="010" when Fin="010"

64

65

else

"001" when Fin="001"

66

67

else

f when Fin="100"

68

69

else

70

f when Fin="100";

71

72

73

--the design of the 2 bit cercuit to compare

74

____

_____

_____

notal: entity work.Inverter(strct) port map(Al,nal);

75

76

77

78

79

nota0: entity work.Inverter(strct) port map(A0,na0);

notbl: entity work.Inverter(strct) port map(B1,nb1);

notb0: entity work.Inverter(strct) port map(B0,nb0);

80

81

-- smaller gates to connect

gl: entity work.ANDG(strct) port map(nal,Bl,a(0));

82

g1: entity work.AND3G(strct) port map(na0,B1,B0,a(1));

g3: entity work.AND3G(strct) port map(na1,na0,B0,a(2));

83

84

85

g4: entity work.OR3G(strct) port map(a(0),a(1),a(2),smaller);

86

87

- equall gates to connect

g5: entity work.XNORG(strct) port map(A1,B1,n(0));

g6: entity work.XNORG(strct) port map(A0,B0,n(1));

88

89

90

g7: entity work.ANDG(strct) port map(n(0),n(1),equall);

91

92

greater gates to connect

93

g8: entity work.ANDG(strct) port map(A1,nb1,a(3));

g9: entity work.AND3G(strct) port map(A0,nb1,nb0,a(4));

g10:entity work.AND3G(strct) port map(A1,A0,nb0,a(5));

94

95

96

gll:entity work.OR3G(strct) port map(a(3),a(4),a(5),greater);

97

98

100

f<=(equall & smaller & greater);</pre>

101

--16 ns delay

end architecture strct;

```

FIGURE 9:2BIT MAGNITUDE COMPARATOR CODE

### > Stage 1

In this stage we were required to make a comparator between A and B using the full adders, so what I did was to get the 2's complement of B by XOR it with 1 and log it into full adder with A, so we will get this formula: A + (-B) = A - B

As a result, the answer if was 0 that means that A and B are equals, on the other hand to know if A>B or A<B I had to solve it and find a function that give me a relation and found this:

|      |        |       | A <b< td=""></b<> |

|------|--------|-------|-------------------|

| 00   | 50m(7) | A>B   | 1.0               |

|      | G      | 1     |                   |

| 0    |        | 0     | 1                 |

| 0    |        | 0     | 1                 |

| 1    | 0      |       |                   |

| 1    | 1      |       |                   |

|      |        |       |                   |

| A>B_ | = 00   | XOR   | 5UM(7)            |

| ASE  | 3 = 01 | 1 XOR | SUM(7)            |

|      |        |       |                   |

### FIGURE 10:COMPARATOR TRUTH TABLE

If the XOR between overflow and the 8th bit of the answer of the summation was 1 this means A<B and if 0 then A>B and applied this as a code.

The next figure shows the code:

```

30

31 library ieee;

32 USE ieee.std_logic_1164.ALL;

33

34 entity comparator is

35     port(clk: in std_logic;

36     A,B: in std_logic_vector(7 downto 0);

37     Fq,Fg,Fs:out std_logic);

38 end entity comparator;

39

```

```

-- the comparator using full adder

-- the comparator using full adder

architecture adder_comport comparator is

signal Bxored, sum: std_logic_vector(7 downto 0);

signal cout6, cout, 00, res.equall : std_logic;

signal fout: std_logic_vector(2 downto 0);

signal fqr, fgr,fsr: std_logic;

43

44

\begin{array}{r} 45\\ 46\\ 47\\ 48\\ 95\\ 51\\ 52\\ 55\\ 55\\ 55\\ 55\\ 55\\ 60\\ 61\\ 63\\ 66\\ 66\\ 68\\ 97\\ 71\\ 77\\ 78\\ 77\\ 78\end{array}

begin

XORB: entity work.XOR subG(strct) port map(B, Bxored); -- to nigative all B digits to be subtracted

entity work.bit8_adder(strct) port map(A, Bxored, '1', sum, cout6, cout); -- 8 bit adder subtractor work

--like subtractor as it has the B is xor with 1 and have a Cin =1 to work as subtract

FA8:

gl: entity work.XORG(strct) port map(cout6, cout, 0v); -- to get the over flow by making xor between the Cout and the previous cout

g2: entity work.XORG(strct) port map(Ov, sum(7), res); -- to check ether it's grater or smaller (A & B)

g3: entity work.NOR8G(strct) port map(sum, equall); -- a nor gate for all summation result index so to know ether the sum =0 or not

Fout<= "100" when equall='1'

else

"001" when res='1'

else

"010" when res='0';

Far<= Fout(2);</pre>

Fgr<= Fout(1);

Fsr<= Fout(0);</pre>

g4: entity work.dfflop(rise_dff) port map(clk,Fqr,Fq);

g5: entity work.dfflop(rise_dff) port map(clk,Fgr,Fg);

g6: entity work.dfflop(rise_dff) port map(clk,Fsr,Fs);

delay needed is 127 ns for this circuit

so th clk will be 127 ns

--clk<= not clk after 127 ns;

end architecture adder_comp;

```

### FIGURE 11:COMPARATOR STAGE 1 CODE

I made XOR gate with "11111111" to negative all B digits to be subtracted

- Then I insert it with A into the 8 bit adder subtractor to work like subtractor as it has the B is xor with 1 and have a Cin =1 to work as subtractor

- Then I XOR the Carry out with the carry out of the previous one to get the overflow

- Then I made XOR between overflow and the last bit of the summation answer to check ether it's greater or smaller (A & B)

- And added a nor gate for all summation result index so to know ether the sum =0 or not

- The delay needed was 127 ns and that's strange a bit.

The simulation of the results was good but with some glitches because O didn't use a register flip flop till now, here is some results

| Signal name            | Value | 488.8                   | • • 4892 • • • 4896 • • • 490 • • • 4904 • • • 4908 • • • 4912 • • • 4916 • • • 492 • • u                                          |

|------------------------|-------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 🕀 🖿 A                  | 19    | X14 X15 X16 X17 X18 X19 | 488 980 678 ps XIE XIF X20 X21 X22 X23 X24 X25 X26 X27 X28 X29 X2A X28 X2C X20 X2E X2F X30 X31 X32 X33 X34 X35 X36 X37 X38 X39 X3A |

| 🕀 🕨 B                  | 8C    | <u>X 8A X 8B X 8C</u>   | X 80 X 8E X 8F X 90 X 91 X 92 X 93 X 94 X 95 X 96 X 97 X 98 X 99 X 9A X 98 X 9C X90                                                |

| ⊞ лг sum               | 8D    |                         |                                                                                                                                    |

| JT cout                | 0     |                         |                                                                                                                                    |

| JUL OV                 | 1     |                         |                                                                                                                                    |

| JU res                 | 0     |                         |                                                                                                                                    |

| 🛥 Fq                   | 0     |                         |                                                                                                                                    |

| 🛥 Fg                   | 1     |                         |                                                                                                                                    |

| <ul> <li>Fs</li> </ul> | 0     |                         |                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Signal name | Value | 484 • • 484.4 • • 484.8 • • 485.2 • • 485.6 • • 486.4 • • 485.8 • • 487.2 •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Barry sum     76     1 (23) (1 (25) (26) (27) (1 (27) (26) (27) (1 (27) (26) (27) (26) (27) (26) (27) (26) (27) (26) (27) (26) (27) (27) (27) (27) (27) (27) (27) (27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 🗄 🍽 A       | EB    | XEX XES XES XES XES XES XEX XEE 484 357 410 ps XF0 XF1 XF2 XF3 XF4 XF5 XF6 XF7 XF8 XF6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Inr cout         1         Inr cout         Inr         Inr         Inr | 🕀 🕨 B       | 75    | X 72 X 73 X 74 X 75 X 76 X 77 X 78 X 79 X 7A X 78 X 70 X 77 X 78 X 79 X 74 X 78 X 77 X 78 X 79 X 74 X 78 X 77 X 78 X 79 X 74 X 78 X 79 X 78 X 79 X 74 X 78 X 79 X 78 X 79 X 74 X 78 X 79 X 78 X 78 |

| Int Ov         1         Int Ov                                                    | ⊞ JTI sum   | 76    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| III res         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JT cout     | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| • Fq 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | JUL OV      | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | JU res      | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| • Fg 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 🛥 Fq        | 0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 🛥 Fg        | 0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| • Fs 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 🛥 Fs        | 1     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

FIGURE 12: STAGE1 OUTPUT

**15 |** Page

### Stage 2

Here we were asked to make the comparator using the magnitude comparator method, so what I did was creating 7-bit magnitude comparator by using the 1-bit and used the 2-bits 3 times and the last bit was the sign bit so there is no need to add it, it's a comparison between 2 digits, if one of them was a negative and the other was positive then the answer will pop up fast but if they both were positive/negative then I have to use the magnitude comparator.

The delay of this circuit was 16 ns and that's good, here is a screenshot of the code:

```

97

architecture mag_comp of comparator is

signal result, s1, s2, s3, Fout: std logic vector(2 downto 0);

99

signal Fqr, Fgr, Fsr: std_logic;

begin

101

102

Fout<="010" when A(7)='1' and B(7)='0'

else

104

"001" when A(7)='0' and B(7)='1'

105

else

106

result when A(7)='1' and B(7)='1'

107

else

108

result when A(7)='0' and B(7)='0';

109

\frac{110}{111}

gl: entity work.one_bit(strct) port map(A(6), B(6), s1);

g2: entity work.two_bit(strct) port map(s1, A(5),A(4), B(5),B(4), s2);

112

g3: entity work.two_bit(strct) port map(s2, A(3),A(2), B(3),B(2), s3);

113

g4: entity work.two_bit(strct) port map(s3, A(1),A(0), B(1),B(0), result);

114

115

Fqr<= Fout(2);</pre>

116

Fsr<= Fout(1);</pre>

Fgr<= Fout(0);</pre>

117

118

119

g5: entity work.dfflop(rise_dff) port map(clk,Fqr,Fq);

g6: entity work.dfflop(rise_dff) port map(clk,Fgr,Fg);

121

g7: entity work.dfflop(rise_dff) port map(clk,Fsr,Fs);

122

123

-- delay needed is 16 ns for this circuit

124

-- so th clk will be 16 ns

125

--clk<= not clk after 16 ns;

126

127

end architecture mag comp;

```

FIGURE 13:COMPARATORE STAGE2 CODE

### The simulation of the results was very good and here is some results

| Signal name  | Value | · · · · · | <br>4 | · · · | <br>8 |   | · ·     | 12    | (1, 1) | 16 | 1.1 | · 2 | 0 | · · | 24 | 1 |   | <br>28 |  | 32 |

|--------------|-------|-----------|-------|-------|-------|---|---------|-------|--------|----|-----|-----|---|-----|----|---|---|--------|--|----|

| <b>∓</b> ► A | 5F    |           |       |       |       |   | 9 572 0 | 72 ps |        |    |     |     |   |     |    |   |   |        |  |    |

| ± ► B        | 2F    |           |       |       |       | L |         |       |        |    |     |     |   |     |    |   |   |        |  |    |

| 🗢 Fg         | 0     |           |       |       |       |   |         |       |        |    |     |     |   |     |    |   |   |        |  |    |

| 🛥 Fg         | 1     |           |       |       |       |   |         |       |        |    |     |     |   |     |    |   |   |        |  |    |

| 🛥 Fs         | 0     |           |       |       |       |   |         |       |        |    |     |     |   |     |    |   | 1 |        |  |    |

#### || 27 27 🕼 및 일 🖓 🖫 웹 瑞田 田 연 억 억 억 억 성 🕷 🕷 🚺 🖡 🛒 🗑 🎆 🖉 着 打 🖬 🖉 🖏 🖏 👘 👘 🖉 👘 👘 👘 👘 👘 👘 👘 👘 👘 👘 👘 👘 👘

| Signal name | Value | · • | 5 <u>0</u> | • | • | 6 | 4 · | <br> | 68 |       |       |    | 72 | ٠ | 76 | • | 1 | 80 | 1 | 1 | 84 | • | 88 | • | L |

|-------------|-------|-----|------------|---|---|---|-----|------|----|-------|-------|----|----|---|----|---|---|----|---|---|----|---|----|---|---|

| 🕀 🖦 A       | A9    |     |            |   |   |   |     |      |    | 68 16 | 5 822 | os |    |   |    |   |   |    |   |   |    |   |    |   | 1 |

| 🕀 🗭 B       | 54    |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   | 1 |

| 🛥 Fq        | 0     |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   |   |

| 🛥 Fg        | 0     |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   | 1 |

| 🛥 Fs        | 1     |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   | 1 |

|             |       |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   |   |

|             |       |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   |   |

|             |       |     |            |   |   |   |     |      |    |       |       |    |    |   |    |   |   |    |   |   |    |   |    |   |   |

#### Reconcernent of the maximum of the second of the second se

| Signal name | Value | · · · · · · · · · · · · · · · · · · ·                                                                     |

|-------------|-------|-----------------------------------------------------------------------------------------------------------|

| 🕀 🍽 A       | FF    | <u>X EE X EF X F0 X F1 X F2 X F3 X F4 X F5 X F6 X F7 X F8 X F9 X FA X F8 X FC X FD X FE X FF X 00 X01</u> |

| 🕀 🗭 B       | FF    | X F7 X F8 X F9 X FA X F8 X FC X FD X FE X FF X 00                                                         |

| 🛥 Fq        | 1     |                                                                                                           |

| 🛥 Fg        | 0     |                                                                                                           |

| 🛥 Fs        | 0     |                                                                                                           |

|             |       |                                                                                                           |

|             |       |                                                                                                           |

|             |       |                                                                                                           |

### FIGURE 14:STAGE2 OUTPUT

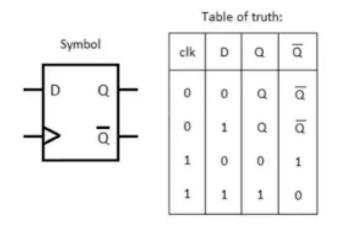

## **D-Flip Flop**

This register works as shown below:

FIGURE 15:D-FLIP FLOP TRUTH TABLE

It was used to get rid of glitches that appears on the comparator to get clear results; the code of DFF is shown below:

```

2

4

-- D Flip Flop to get off delays

5

library ieee;

6

use ieee.std_logic_1164.all;

7

8

entity dfflop is

port(clk, d:in std_logic;

9

o : out std logic );

10

11

end entity dfflop;

12

13

14

architecture rise_dff of dfflop is

15

begin

16

process(clk)

17

begin

18

if(rising_edge(clk)) then

19

o <= d;

end if;

20

21

end process;

22

end rise_dff;

22

```

### FIGURE 16: D FLIP-FLOP CODE

It solved the glitches, and therefore it was added in every stage with a controlled clock by the Built In Self-Test.

### **Test Generator**

This generator contains a clock input, A, B inputs, and the proper output. Its design comprises two processes: the first produces the correct output in behavioral logic, and the second modifies (increments) the values of A and B as the clock input increases to reach all conceivable inputs.

```

----- Test Generator -----

83

84

LIBRARY ieee;

85

USE ieee.std_logic_1164.ALL;

USE ieee.std_logic_ARITH.ALL;

86

87

88

USE ieee.std_logic_UNSIGNED.ALL;

89

90

91

ENTITY TestGenerator IS

PORT(clk: IN STD_LOGIC:='0';

A,B: OUT STD_LOGIC_VECTOR(7 DOWNTO 0):="000000000";

FqCorr, FgCorr, FsCorr: OUT STD_LOGIC:='0');

92

93

94

95

END TestGenerator;

96

97

98

99

ARCHITECTURE generator OF TestGenerator IS

SIGNAL AA,BB: STD_LOGIC_VECTOR(7 DOWNTO 0):="00000000";

SIGNAL x: STD_LOGIC_VECTOR(2 DOWNTO 0):="000";

BEGIN

\Delta < = \Delta \Delta:

B<=BB:

104

FqCorr<=X(2);</pre>

FgCorr<=X(1);

106

107

FsCorr<=X(0);

108

-- The Process Below calculate the behavioural results

PROCESS (clk)

BEGIN

114

if (AA = BB) then

115

x<="100";

110

111

112

113

114

115

116

PROCESS (clk)

BEGIN

if (AA = BB) then

x<="100";

elsif (AA > BB) then

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

elsif (AA < BB) then

x<="001";

end if;

END PROCESS;

-- this 2 loops to make sure to check all the possible results between A and B

PROCESS

FOR i IN 0 TO 255 LOOP

FOR j IN 0 TO 255 LOOP

AA(7 DOWNTO 0) <= CONV_STD_LOGIC_VECTOR(i,8);

BB(7 DOWNTO 0) <= CONV_STD_LOGIC_VECTOR(j,8);</pre>

WAIT UNTIL rising_edge(CLK);

END LOOP;

END LOOP;

WAIT;

END PROCESS

138

139

END:

```

### FIGURE 17:TEST CODE

And the outputs of random A and B will go to the circuit I made to be calculated and the result will be compared with the correct ones that had been solved, this will happen in the next level which is called result analyzer.

## **Result Analyzer**

When the clock input increases as illustrated, this analyzer confirms that the outputs are proper. If not, it will give an error message. Here is the code:

```

164

165

----- Result Analyser -----

166

_____

167

LIBRARY ieee:

168 USE ieee.std_logic_1164.ALL;

169 USE ieee.std_logic_ARITH.ALL;

170

171

172 ENTITY ResultAnalyser IS

173 PORT(CLK: IN STD_LOGIC:='0';

Fqc, Fgc, Fsc, Fq, Fg, Fs: IN STD_LOGIC:='0');

END ResultAnalyser;

174

175

176

177

178

ARCHITECTURE analyser OF ResultAnalyser IS

179

BEGIN

180

-- The code below is to make sure that the result from my system equals to the correct one or not

-- if not it will print an error when the outputs are not equal to each other

181

PROCESS

182

183

BEGIN

184

assert (Fqc = Fq and Fgc = Fg and Fsc = Fs)

185 report "The results that were obtained from your design don't agree with the correct results"

186 severity ERROR;

187 WAIT UNTIL rising_edge(CLK);

188 END PROCESS;

189

END;

190

```

FIGURE 18:RESULT ANALYZER CODE

## **Built in Self-Test**

This entity has the whole system with a test generator and result analyzer, as illustrated in Figure - in two phases. The clock signal inverses after a set period, and the test generator changes A and B signals and sends the right output to the result analyzer. The outputs A and B are sent to the system, which generates an output. This output is then sent to the result analyzer, which determines whether or not the output is valid based on the test generator's proper result. The clock signal for the generator and analyzer will be the same. The delay is the difference between the two phases.

224 -----225 ----- Built In Self Test -----226 \_\_\_\_\_ 227 LIBRARY ieee; 228 USE ieee.std\_logic\_1164.ALL; 229 USE ieee.std\_logic\_ARITH.ALL; ENTITY BIST IS 230 231 END ENTITY BIST; 232 233 ----- Test For The adder comparator -----234 ARCHITECTURE adder\_comp OF BIST IS 235 236 SIGNAL clk: STD\_LOGIC:='0'; SIGNAL A,B: STD\_LOGIC\_VECTOR(7 DOWNTO 0):="00000000": 237 SIGNAL Fq, Fg, Fs,Fqc, Fgc, Fsc: STD\_LOGIC:='0'; 238 239 BEGIN 240 241 -- 127 ns is the minimum delay we should have to have a correct output 242 -- so I'll increse it 3 ns to make sure of the of the correct answer 243 CLK <= NOT CLK AFTER 130 NS; 244 245 246 G1: ENTITY WORK.TestGenerator(generator) PORT MAP(clk, A, B, Fqc, Fgc, Fsc); 247 248 G2: ENTITY WORK.comparator(adder\_comp) PORT MAP(clk, A, B, Fq, Fg, Fs); 249 250 G3: ENTITY WORK.ResultAnalyser(analyser) PORT MAP(clk, Fqc, Fqc, Fsc, Fq, Fg, Fs); 251 252 END ARCHITECTURE adder comp; 253

FIGURE 19:BUILT IN SELF TEST CODE FOR ADDER COMPARATOR

265 266 ----- Test For The magnitude comparator ------267 ARCHITECTURE mag\_comp OF BIST IS 268 SIGNAL clk: STD\_LOGIC:='0'; 269 SIGNAL A,B: STD\_LOGIC\_VECTOR(7 DOWNTO 0):="00000000"; 270 271 SIGNAL Fq, Fg, Fs, Fqc, Fgc, Fsc: STD LOGIC:='0'; 272 BEGIN 273 -- 16 ns is the minimum delay we should have to have a correct output 274 275 -- so I'll increse it 3 ns to make sure of the of the correct answer 276 277 CLK <= NOT CLK AFTER 19 NS; 278 279 G1: ENTITY WORK.TestGenerator(generator) PORT MAP(clk, A, B, Fqc, Fgc, Fsc); 280 G2: ENTITY WORK.comparator(mag comp) PORT MAP(clk, A, B, Fq, Fg, Fs); 281 282 283 G3: ENTITY WORK.ResultAnalyser(analyser) PORT MAP(clk, Fqc, Fgc, Fsc, Fq, Fg, Fs); 284 285 END ARCHITECTURE mag\_comp; 286 287

FIGURE 20:BUILT IN SELF-TEST CODE FOR MAGNITUDE COMPARATOR

# Results

## Stage 1

We can see that the shortest period to avoid delay issues is 127 nanoseconds, and it will not display an error. Therefore, I increase it by 3 ns to make sure.

The outcomes of the simulation, as well as the discrepancy between the behavioral output and the actual output, are shown in these images.

| Signal name | Value | 800 |   | 1000 | 1200 |    | 1400 | 1600 | 1 I. | 1800 | 2000 | 1 A. | 2200 | 240 | 0 · 0    | · · |

|-------------|-------|-----|---|------|------|----|------|------|------|------|------|------|------|-----|----------|-----|

| лг dk       | 0     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

| A 17. 🕀     | 00    |     |   |      |      |    |      | (    | 00   |      |      |      |      |     |          |     |

| ⊕лл B       | 73    | 03  | X | 04   | X    | 05 |      | 06   | X    | 07   | _X   | 08   | X    | 09  | <u> </u> | 0A  |

| лг Fq       | 0     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

| лг Fg       | 0     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

| лг Fs       | 1     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

| JU Fqc      | 0     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

| JUT Fgc     | 0     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

| ли Fsc      | 1     |     |   |      |      |    |      |      |      |      |      |      |      |     |          |     |

FIGURE 21:SIMULATION OUTCOMES

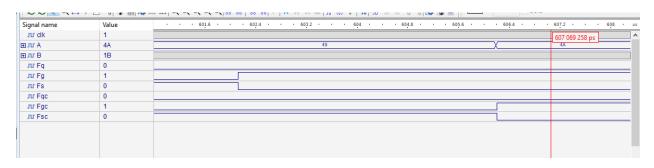

## Stage 2

We can see that the shortest period to avoid delay issues is 16 nanoseconds, and it will not display an error. Therefore, I increase it by 3 ns to make sure.

The outcomes of the simulation, as well as the discrepancy between the behavioral output and the actual output, are shown in these images.

| Signal name | Value | · · · 75.2 · · · 76 · · · 76.8 · · · 77.6 · · · 78.4 · · · 79.2 · · · 80 · · · 80.8 · · · 81.6 · us |

|-------------|-------|-----------------------------------------------------------------------------------------------------|

| JUL CIK     | 0     | 76 487 902 ps                                                                                       |

| A 17. 🕀     | 09    | 09                                                                                                  |

| ⊞ JUL B     | 56    |                                                                                                     |

| лг Fq       | 0     |                                                                                                     |

| лг Fg       | 0     |                                                                                                     |

| лгFs        | 1     |                                                                                                     |

| лг Еqc      | 0     |                                                                                                     |

| лг Fgc      | 0     |                                                                                                     |

| лг Fsc      | 1     |                                                                                                     |

|             |       |                                                                                                     |

|             |       |                                                                                                     |

|             |       |                                                                                                     |

|             |       |                                                                                                     |

### FIGURE 22: OUTCOME OF THE SIMULATION

And I tried to create an error on purpose to check if this is working well or not

## **Conclusion and Future works**

The outcomes of the preceding operations are consistent with the theoretical results. Furthermore, we infer that we can build large systems using smaller ones.

We successfully construct an 8-bit signed comparator and then write a functioning verification method. We discovered that the built-in test is helpful in ensuring that the results are accurate.

In our system, we learnt about two kinds of adders and saw the difference between the ripple full adder and the carry lookahead adder since it cuts latency significantly. Because the carry of each 1-bit complete adder is independent of the preceding carries save the first, the lookahead adder is quicker than the ripple adder, so we knew what the differences are between the 2 stages.

And how the full adder can be implemented to work in much things.

And how useful it is to use the small blocks instead of creating one huge entity.

We learned more about VHDL and how to create commands such as printing an error, delaying a signal, testing systems, and creating entities in behavioral and structural logics. We also used Aldec HDL to simulate our project and observe the signals of the entity on which we worked.

# References

- [1] "GeeksForGeeks," 19 Feb 2021. [Online]. Available: https://www.geeksforgeeks.org/magnitudecomparator-in-digital-logic/. [Accessed 24 12 2021].

- [2] "UIC Computer Science," [Online]. Available: https://www.cs.uic.edu/~i266/hwk6/42.pdf.

# Appendix

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity Inverter is

port(a: in std\_logic;

b: out std\_logic);

end entity Inverter;

architecture strct of Inverter is

begin

b<= not a after 2 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity NANDG is

port(a,b: in std\_logic;

c: out std\_logic);

end entity NANDG;

architecture strct of NANDG is

begin

c<= a nand b after 5 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity NORG is

port(a,b: in std\_logic;

c: out std\_logic);

end entity NORG;

architecture strct of NORG is

begin

c<= a nor b after 5 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity ANDG is

port(a,b: in std\_logic;

c: out std\_logic);

end entity ANDG;

architecture strct of ANDG is

begin

c<= a and b after 7 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity ORG is

port(a,b: in std\_logic;

c: out std\_logic);

end entity ORG;

architecture strct of ORG is

begin

```

c<= a or b after 7 ns;

```

end architecture strct;

\_\_\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity XNORG is

port(a,b: in std\_logic;

c: out std\_logic);

end entity XNORG;

architecture strct of XNORG is

begin

c<= a xnor b after 9 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity XORG is

port(a,b: in std\_logic;

c: out std\_logic);

end entity XORG;

architecture strct of XORG is

begin

c<= a xor b after 12 ns;

end architecture strct;

\_\_\*\*\*\*\*\*\*\*\*

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity AND3G is

port(a,b,d: in std\_logic;

c: out std\_logic);

end entity AND3G;

architecture strct of AND3G is

begin

c<= a and b and d after 7 ns;

end architecture strct;

\_\_\*\*\*\*\*\*\*\*\*\*

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity OR3G is

port(a,b,d: in std\_logic;

c: out std\_logic);

end entity OR3G;

architecture strct of OR3G is

begin

c<= a or b or d after 7 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity XOR\_subG is

port(a: in std\_logic\_vector(7 downto 0);

c: out std\_logic\_vector(7 downto 0));

end entity XOR\_subG;

architecture strct of XOR\_subG is

begin

c<= a xor "11111111" after 12 ns;

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity NOR8G is

port(a: in std\_logic\_vector(7 downto 0);

c: out std\_logic);

end entity NOR8G;

architecture strct of NOR8G is

signal s: std\_logic;

begin

s<= a(0) or a(1) or a(2) or a(3) or a(4) or a(5) or a(6) or a(7);

c<= not s after 5 ns;

end architecture strct;

-- one bit full adder circuit

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity FA is

port(A,B,Cin:in std\_logic;

s,Cout:out std\_logic);

end entity FA;

architecture one\_bit\_adder of FA is

signal s1,s2,s3,s4,s5: std\_logic;

begin

- g1: entity work.XORG(strct) port map(A,B,s1);

- g2: entity work.ANDG(strct) port map(A,B,s2);

g3: entity work.ANDG(strct) port map(Cin,s1,s3);

- g4: entity work.XORG(strct) port map(s1,Cin,s4);

- g5: entity work.ORG(strct) port map(s2,s3,s5);

s<=s4;

Cout<=s5;

--24 ns needed to give correct answer

end architecture one\_bit\_adder;

--8 bits full adder

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity bit8\_adder is

port(A,B:in std\_logic\_vector(7 downto 0); Cin:in std\_logic; sum:out std\_logic\_vector(7 downto 0); Cout6, Cout:out std\_logic);

end entity bit8\_adder;

architecture strct of bit8\_adder is

signal s,c:std\_logic\_vector(7 downto 0);

### begin

g1: entity work.FA(one\_bit\_adder) port map(A(0),B(0),Cin,s(0),c(0));

g2: entity work.FA(one\_bit\_adder) port map(A(1),B(1),c(0),s(1),c(1));

g3: entity work.FA(one\_bit\_adder) port map(A(2),B(2),c(1),s(2),c(2));

g4: entity work.FA(one\_bit\_adder) port map(A(3),B(3),c(2),s(3),c(3));

g5: entity work.FA(one\_bit\_adder) port map(A(4),B(4),c(3),s(4),c(4));

g6: entity work.FA(one\_bit\_adder) port map(A(5),B(5),c(4),s(5),c(5));

g7: entity work.FA(one\_bit\_adder) port map(A(6),B(6),c(5),s(6),c(6));

g8: entity work.FA(one\_bit\_adder) port map(A(7),B(7),c(6),s(7),c(7));

Cout6<=c(6);

Cout<=c(7);

sum<=s;

-- 24 ns needed for delay correction

end architecture strct;

--entities to make the magnitude comparator

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity one\_bit is

port(a,b: in std\_logic;

F:out std\_logic\_vector(2 downto 0));

end entity one\_bit;

architecture strct of one\_bit is

signal s1,s2,s3,s4,s5:std\_logic;

begin

g1: entity work.Inverter(strct) port map(A,s1);

g2: entity work.Inverter(strct) port map(B,s2);

g3: entity work.ANDG(strct) port map(B,s1,s3); --A<B

g4: entity work.ANDG(strct) port map(A,s2,s4); --A>B

g5: entity work.NORG(strct) port map(s3,s4,s5); --A=B

F<=(s5 & s3 & s4);

-- 14 ns delay

end architecture strct;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity two\_bit is

port(Fin: in std\_logic\_vector(2 downto 0);

a1,a0,b1,b0: in std\_logic;

Fout:out std\_logic\_vector(2 downto 0));

end entity two\_bit;

architecture strct of two\_bit is

signal na1,na0,nb1,nb0:std\_logic; signal a:std\_logic\_vector(5 downto 0); signal n:std\_logic\_vector(1 downto 0); signal smaller, equall, greater: std\_logic; signal f: std\_logic\_vector(2 downto 0);

### begin

-- compare if the previous bits are greater to pass the answer or not to start calculating

Fout<="010" when Fin="010"

#### else

```

"001" when Fin="001"

```

else

```

f when Fin="100"

```

else

```

f when Fin="100";

```

--the design of the 2 bit cercuit to compare

nota1: entity work.Inverter(strct) port map(A1,na1); nota0: entity work.Inverter(strct) port map(A0,na0); notb1: entity work.Inverter(strct) port map(B1,nb1); notb0: entity work.Inverter(strct) port map(B0,nb0);

-- smaller gates to connect

- g1: entity work.ANDG(strct) port map(na1,B1,a(0));

- g2: entity work.AND3G(strct) port map(na0,B1,B0,a(1));

- g3: entity work.AND3G(strct) port map(na1,na0,B0,a(2));

- g4: entity work.OR3G(strct) port map(a(0),a(1),a(2),smaller);

-- equall gates to connect

- g5: entity work.XNORG(strct) port map(A1,B1,n(0));

- g6: entity work.XNORG(strct) port map(A0,B0,n(1));

- g7: entity work.ANDG(strct) port map(n(0),n(1),equall);

-- greater gates to connect

- g8: entity work.ANDG(strct) port map(A1,nb1,a(3));

- g9: entity work.AND3G(strct) port map(A0,nb1,nb0,a(4));

g10:entity work.AND3G(strct) port map(A1,A0,nb0,a(5));

g11:entity work.OR3G(strct) port map(a(3),a(4),a(5),greater);

f<=(equall & smaller & greater);

--16 ns delay

end architecture strct;

-- D Flip Flop to get off delays library ieee;

use ieee.std\_logic\_1164.all;

entity dfflop is

port(clk, d:in std\_logic;

```

o : out std_logic );

```

end entity dfflop;

architecture rise\_dff of dfflop is

begin

process(clk)

begin

```

if(rising_edge(clk)) then

```

o <= d;

end if;

end process;

end rise\_dff;

library ieee;

USE ieee.std\_logic\_1164.ALL;

entity comparator is

port(clk: in std\_logic;

A,B: in std\_logic\_vector(7 downto 0);

Fq,Fg,Fs:out std\_logic);

end entity comparator;

-- the comparator using full adder architecture adder\_comp of comparator is signal Bxored, sum: std\_logic\_vector(7 downto 0); signal cout6, cout, Ov, res,equall : std\_logic; signal Fout: std\_logic\_vector(2 downto 0); signal fqr, fgr,fsr: std\_logic;

#### begin

XORB: entity work.XOR\_subG(strct) port map(B, Bxored); -- to nigative all B digits to be subtracted

FA8: entity work.bit8\_adder(strct) port map(A, Bxored, '1', sum, cout6, cout); - 8 bit adder subtractor work

--like subtractor as it has the B is xor with 1 and have a Cin =1 to work as subtract

g1: entity work.XORG(strct) port map(cout6, cout, Ov); -- to get the over flow by making xor between the Cout and the previous cout

g2: entity work.XORG(strct) port map(Ov, sum(7), res); -- to check ether it's grater or smaller (A & B)

g3: entity work.NOR8G(strct) port map(sum, equall); -- a nor gate for all summation result index so to know ether the sum =0 or not

Fout<= "100" when equall='1'

else

```

"001" when res='1'

```

else

```

"010" when res='0';

```

```

Fqr \le Fout(2);

```

Fgr<= Fout(1);

Fsr<= Fout(0);

g4: entity work.dfflop(rise\_dff) port map(clk,Fqr,Fq);

g5: entity work.dfflop(rise\_dff) port map(clk,Fgr,Fg);

g6: entity work.dfflop(rise\_dff) port map(clk,Fsr,Fs);

-- delay needed is 127 ns for this circuit

-- so th clk will be 127 ns

--clk<= not clk after 127 ns;

end architecture adder\_comp;

-- the comparator using magnitude comparator

architecture mag\_comp of comparator is

signal result, s1, s2, s3, Fout: std\_logic\_vector(2 downto 0);

signal Fqr, Fgr, Fsr: std\_logic;

begin

```

Fout<="010" when A(7)='1' and B(7)='0'

```

else

```

"001" when A(7)='0' and B(7)='1'

```

else

```

result when A(7)='1' and B(7)='1'

```

else

```

result when A(7)='0' and B(7)='0';

```

g1: entity work.one\_bit(strct) port map(A(6), B(6), s1);

g2: entity work.two\_bit(strct) port map(s1, A(5),A(4), B(5),B(4), s2);

g3: entity work.two\_bit(strct) port map(s2, A(3),A(2), B(3),B(2), s3);

g4: entity work.two\_bit(strct) port map(s3, A(1),A(0), B(1),B(0), result);

Fqr<= Fout(2);

Fsr<= Fout(1);

Fgr<= Fout(0);

g5: entity work.dfflop(rise\_dff) port map(clk,Fqr,Fq);

- g6: entity work.dfflop(rise\_dff) port map(clk,Fgr,Fg);

- g7: entity work.dfflop(rise\_dff) port map(clk,Fsr,Fs);

-- delay needed is 16 ns for this circuit

-- so th clk will be 16 ns

--clk<= not clk after 16 ns;

end architecture mag\_comp;

--islam jihad 1191375

library ieee;

USE ieee.std\_logic\_1164.ALL;

use IEEE.STD\_LOGIC\_ARITH.ALL;

use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

entity testbanch is end;

architecture test of testbanch is

signal testa,testb:std\_logic\_vector(7 downto 0):="00000000"; signal sum: std\_logic\_vector(7 downto 0); signal cin:std\_logic:='0'; signal cout: std\_logic; begin

g1: entity work.bit8\_adder(strct) port map(testa, testb,cin,sum,cout);

testa<=testa + 1 after 200 ns; testb<=testb + 1 after 400 ns; cin<= not cin after 800 ns;

end;

library ieee;

USE ieee.std\_logic\_1164.ALL;

use IEEE.STD\_LOGIC\_ARITH.ALL;

use IEEE.STD\_LOGIC\_UNSIGNED.ALL;

entity testbanch1 is

end;

architecture test of testbanch1 is

signal testa,testb:std\_logic\_vector(7 downto 0):="00000000"; signal ans: std\_logic\_vector(2 downto 0); signal Fq, Fs, Fg,clk: std\_logic; begin

g1: entity work.mag\_comp(strct) port map(clk, testa, testb,Fq, Fs, Fg);

testa<=testa + 1 after 200 ns; testb<=testb + 1 after 400 ns;

end;

\_\_\_\_\_

----- Test Generator ------

-----

LIBRARY ieee;

USE ieee.std\_logic\_1164.ALL;

USE ieee.std\_logic\_ARITH.ALL;

USE ieee.std\_logic\_UNSIGNED.ALL;

**ENTITY TestGenerator IS**

PORT(clk: IN STD\_LOGIC:='0';

A,B: OUT STD\_LOGIC\_VECTOR(7 DOWNTO 0):="00000000";

FqCorr, FgCorr, FsCorr: OUT STD\_LOGIC:='0');

END TestGenerator;

ARCHITECTURE generator OF TestGenerator IS

SIGNAL AA,BB: STD\_LOGIC\_VECTOR(7 DOWNTO 0):="00000000";

SIGNAL x: STD\_LOGIC\_VECTOR(2 DOWNTO 0):="000";

BEGIN

A<=AA; B<=BB; FqCorr<=X(2); FgCorr<=X(1); FsCorr<=X(0); -- The Process Below calculate the behavioural results

```

PROCESS (clk)

```

BEGIN

if (AA = BB) then x<="100"; elsif (AA > BB) then x<="010"; elsif (AA < BB) then x<="001"; end if;

END PROCESS;

-- this 2 loops to make sure to check all the possible results between A

and B

PROCESS

BEGIN

FOR i IN 0 TO 255 LOOP

FOR j IN 0 TO 255 LOOP

CONV\_STD\_LOGIC\_VECTOR(i,8);

AA(7 DOWNTO 0) <=

BB(7 DOWNTO 0) <=

CONV\_STD\_LOGIC\_VECTOR(j,8);

47 | Page

# WAIT UNTIL rising\_edge(CLK);

## END LOOP;

## END LOOP;

# WAIT;

# END PROCESS;

END;

\_\_\_\_\_

----- Result Analyser ------

-----

LIBRARY ieee;

USE ieee.std\_logic\_1164.ALL;

USE ieee.std\_logic\_ARITH.ALL;

ENTITY ResultAnalyser IS

PORT(CLK: IN STD\_LOGIC:='0';

Fqc, Fgc, Fsc, Fq, Fg, Fs: IN STD\_LOGIC:='0');

END ResultAnalyser;

ARCHITECTURE analyser OF ResultAnalyser IS

### BEGIN

-- The code below is to make sure that the result from my system equals to the correct one or not

-- if not it will print an error when the outputs are not equal to each other

PROCESS

#### BEGIN

assert (Fqc = Fq and Fgc = Fg and Fsc = Fs)

report "The results that were obtained from your design don't agree with the correct results"

severity ERROR;

WAIT UNTIL rising\_edge(CLK);

END PROCESS;

END;

-----

----- Built In Self Test ------

-----

LIBRARY ieee;

USE ieee.std\_logic\_1164.ALL;

USE ieee.std\_logic\_ARITH.ALL;

ENTITY BIST IS

END ENTITY BIST;

\_\_\_\_\_

----- Test For The adder comparator ------

ARCHITECTURE adder\_comp OF BIST IS

SIGNAL clk: STD\_LOGIC:='0';

SIGNAL A,B: STD\_LOGIC\_VECTOR(7 DOWNTO 0):="00000000";

SIGNAL Fq, Fg, Fs, Fqc, Fgc, Fsc: STD\_LOGIC:='0';

BEGIN

-- 127 ns is the minimum delay we should have to have a correct output

-- so I'll increse it 3 ns to make sure of the of the correct answer

CLK <= NOT CLK AFTER 130 NS;

G1: ENTITY WORK.TestGenerator(generator) PORT MAP(clk, A, B, Fqc, Fgc, Fsc);

G2: ENTITY WORK.comparator(adder\_comp) PORT MAP(clk, A, B, Fq, Fg, Fs);

G3: ENTITY WORK.ResultAnalyser(analyser) PORT MAP(clk, Fqc, Fgc, Fsc, Fq, Fg, Fs);

END ARCHITECTURE adder\_comp;

\_\_\_\_\_

----- Test For The magnitude comparator ------

ARCHITECTURE mag\_comp OF BIST IS

SIGNAL clk: STD\_LOGIC:='0';

SIGNAL A,B: STD\_LOGIC\_VECTOR(7 DOWNTO 0):="00000000";

SIGNAL Fq, Fg, Fs, Fqc, Fgc, Fsc: STD\_LOGIC:='0';

BEGIN

-- 16 ns is the minimum delay we should have to have a correct output

-- so I'll increse it 3 ns to make sure of the of the correct answer

CLK <= NOT CLK AFTER 16 NS;

G1: ENTITY WORK.TestGenerator(generator) PORT MAP(clk, A, B, Fqc, Fgc, Fsc);

G2: ENTITY WORK.comparator(mag\_comp) PORT MAP(clk, A, B, Fq, Fg, Fs);

G3: ENTITY WORK.ResultAnalyser(analyser) PORT MAP(clk, Fqc, Fgc, Fsc, Fq, Fg, Fs);

END ARCHITECTURE mag\_comp;

52 | Page